VLSI – Design For Test (DFT)- JTAG, Boundary SCAN and IJTAG

This course provides detailed concepts on JTAG, Boundary Scan, and IJTAG, along with examples. It covers IEEE1149.1 and IEEE 1687-2014 standards, explaining the operation of the JTAG TAP state machine and its use in connectivity testing. The course also discusses IJTAG operation, ICL, and PDL concepts. Suitable for VLSI aspirants, DFT engineers, and design engineers. Enhance your knowledge of DFT with this comprehensive course.

What you’ll learn

- IJTAG, JTAG and BSDL. DFT concepts

This course talks about detailed concepts on JTAG, Boundary Scan and IJTAG with several examples.

This course teaches in-depth details on IEEE1149.1 and IEEE 1687-2014 standard.

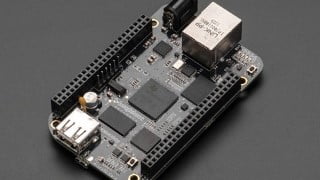

You will also learn about how JTAG TAP state machine operates and how it is used to do connectivity test between difference chips in Printed Circuit Board (PCB)

The IJTAG operation, ICL and PDL concepts are also discussed in this course.

Who this course is for:

- VLSI aspirants, DFT engineers, Design Engineers

User Reviews

Be the first to review “VLSI – Design For Test (DFT)- JTAG, Boundary SCAN and IJTAG”

You must be logged in to post a review.

There are no reviews yet.